8位元16位元的問題,我們搜遍了碩博士論文和台灣出版的書籍,推薦寫的 像素百景:進入點陣圖藝術的世界 可以從中找到所需的評價。

另外網站數位資料表示法也說明:▫ UTF-8(以8位元為基本編碼單元的Unicode Translation Format)vs. UTF-16(以16位元為基本編碼單元的Unicode Translation Format). ▫ 在UTF-8 ...

南台科技大學 電子工程系 薛雲太所指導 張冠程的 設計與實作電流模式快速數位加法器 (2012),提出8位元16位元關鍵因素是什麼,來自於前瞻進位加法器、快速加法器、加法器、電流加法器。

而第二篇論文國立臺灣科技大學 電子工程系 林銘波所指導 袁民倫的 高速冗餘布氏乘法器設計與驗證 (2010),提出因為有 冗餘數字系統、基底-4布氏演算法、基底-16布氏演算法、布氏乘法器的重點而找出了 8位元16位元的解答。

最後網站測驗卷題目+解答- 一、填充題 - 一、 是非題(50%) 注意:答錯 ...則補充:位元 的英文名稱bit,是的簡稱。 ... UTF-16 編碼方式以幾個位元為基本單元? ... 假設一個整數儲存為8 個位元(8-bit memory location),請填入下列空格:. 【解答】.

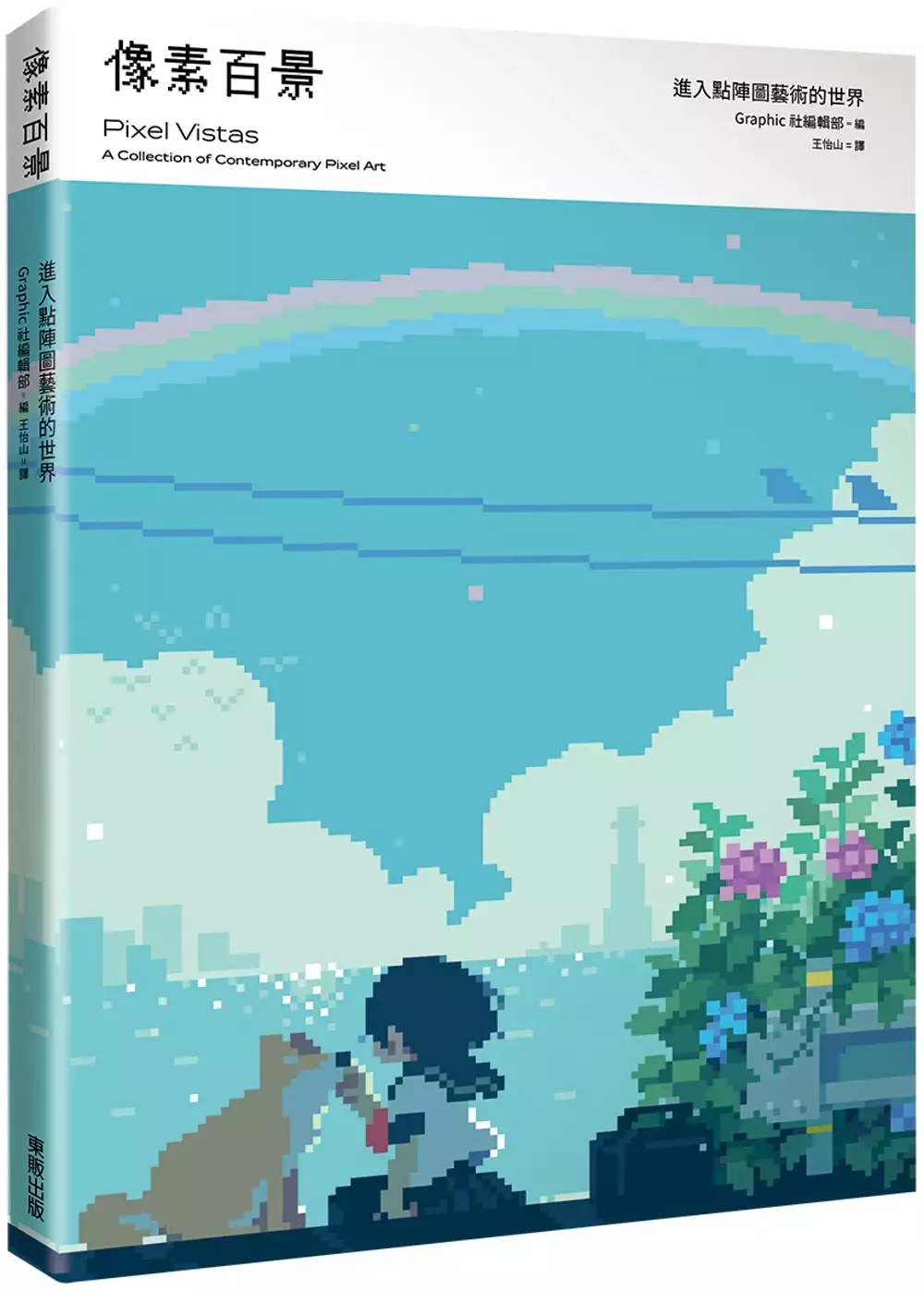

像素百景:進入點陣圖藝術的世界

為了解決8位元16位元 的問題,作者 這樣論述:

歡迎來到像素畫的世界── 所謂的像素,指的是螢幕上的最小單位「像素(Pixel)」,而像素藝術即是以這個最小單位描繪而成的平面作品。 對於喜愛、曾經歷過70~90年代遊戲的人來說,「點陣圖」這個詞或許更令人熟悉。由於當時的螢幕畫面色彩數與解析度有限,角色與風景又必須描繪在8×8或16×16的圖像單元內,因此在美術表現上發展出了獨特的技法。 儘管現在的硬體技術日新月異,進化成了高解析度的3D畫面,以像素為基礎的平面圖像成了「舊時代」的產物,但過時的科技轉化成了藝術,像素的表現手法在懷舊的情懷下形成獨樹一格的藝術類型,透過網路催生出更多自由多樣的作品。 本書

將日本國內外48位主要藝術家的作品集結成冊,透過這些作品、訪談與評論,統整了2010年代後期的像素藝術與其文化變遷,值得細細品味。 本書特色 ●全台唯一講述、分享現代像素(Pixel)藝術的書籍 ●收錄48位現代像素藝術家、超過300張作品

8位元16位元進入發燒排行的影片

末日Z戰:劫後餘生 STEAM版第一日

RTX3090 4K 60FPS | RYZEN 7 5800X

#軒仔遊戲店 #WWZ #STEAM

--

GPU:索泰 NVIDIA RTX 3090 24GB

CPU:AMD Ryzen7 5800X 8C16T

塔散: Scythe 鐮刀Mugen 5 無限五

記憶體:美光Ballistix 16GB DDR4-3200

主機板:Gigabyte 450 AORUS ELITE

(Re-Size BAR ON+AMD AGESA ComboV2 1.2.0.2)

POWER:ENERMAX白金冰核1200W

作業系統:WINDOWS 10 64位元

CASE: CM STORM Trooper遊騎兵

設計與實作電流模式快速數位加法器

為了解決8位元16位元 的問題,作者張冠程 這樣論述:

傳統式的數位加法器,最快速的實作方式為前瞻進位加法器(CLA),但CLA加法器位元數變大時,所需的邏輯電路面積也跟著變大,計算進位的延遲也將變大。本論文利用電流相加的方式試圖簡化進位計算所需的電路與減少進位計算的延遲,本設計首先將數位加法器之邏輯輸入利用電流鏡方式轉為電流,再利用柯希荷夫電流定理將輸入電流相加之後,其次使用比較器計算進位,如此每一級的進位,彼此互相獨立,沒有延遲的問題。而計算的瓶頸主要在於比較器,本論文將以四位元數位加法器為例,說明此電路運行方式,理論上本設計也可以應用於更高位元數的加法器,如8位元、16位元及32位元等。本論文的設計方式,使用TSMC CMOS 0.18μm

RF製程程式庫與Hspice模擬4位元數位加法器,可得最快速度約為666MHz,理論上更高位元數所得的計算速度應該相同,將不因位元數增加而減少,此特性將使本設計在高位元數之數位加法器的應用上具有優勢,另外發現本設計的速度限制在於低電流比較器的速度,若能克服此問題,將可本設計的計算速度加快,另一方面高位元數的加法器也將受限於低電流比較器,因此低電流比較器在本設計上至為重要。

高速冗餘布氏乘法器設計與驗證

為了解決8位元16位元 的問題,作者袁民倫 這樣論述:

在本篇論文中,我們設計並實現了使用冗餘數字系統的布氏乘法器。此布氏乘法器依據基底-4有號數布氏演算法與基底-16有號數布氏演算法並使用正負旗標補數冗餘編碼。為了改善冗餘布氏乘法器效能,我們改進了冗餘布氏乘法器的編碼元件以及壓縮樹元件,並使用了一個高速的冗餘編碼轉一般二補數數字系統轉換器來提升整體效能。本論文也在此兩種不同的冗餘布氏基底上實現了8位元,16位元,24位元,32位元,48位元及64位元共十二種不同基底與資料寬度的冗餘布氏乘法器組合,並且進一步探討相異基底與資料寬度之間對於效能、功率以及硬體消耗的影響。基底-4 16位元冗餘布氏乘法器與基底-16 16位元冗餘布氏乘法器已經分別在X

ilinx Virtex-5 ML505-V5LX110T FPGA以及TSMC 0.18 μm元件庫上實現。在FPGA實現部份,16位元的基底-4冗餘布氏乘法器與基底-16冗餘布氏乘法器分別使用了786與761的LUTs,最高操作頻率皆可達到100 MHz。在元件庫實現部份,兩個冗餘布氏乘法器晶片核心面積皆約為600×630 μm2,整體晶片面積約為970×1000 μm2在100 MHz輸入頻率的操作下,基底-4冗餘布氏乘法器的平均耗電量為1.75 mW,基底-16冗餘布氏乘法器的平均耗電量為1.58 mW。

8位元16位元的網路口碑排行榜

-

#1.8位元與32位元的MCU單晶片差在哪?為您的產品選擇合適的單 ...

MCU單晶片在位元配置方面有8位元、16位元和32位元,但我們在文章當中只會探討8位元 ... 8位元MCU單晶片基本上用於執行簡單的邏輯運算,例如像是加、減、乘、除等運算 ... 於 official.kaijui-tech.com -

#2.常見問題 - 健豪雲端數位網

我發印時到底要使用CMYK還是RGB呢? 影像軟體製稿中,需先選定正確的色彩模式,例如印刷為主要選擇CMYK、8 位元模式, ... 於 gainhow.tw -

#3.數位資料表示法

▫ UTF-8(以8位元為基本編碼單元的Unicode Translation Format)vs. UTF-16(以16位元為基本編碼單元的Unicode Translation Format). ▫ 在UTF-8 ... 於 ccf.ee.ntu.edu.tw -

#4.測驗卷題目+解答- 一、填充題 - 一、 是非題(50%) 注意:答錯 ...

位元 的英文名稱bit,是的簡稱。 ... UTF-16 編碼方式以幾個位元為基本單元? ... 假設一個整數儲存為8 個位元(8-bit memory location),請填入下列空格:. 【解答】. 於 math.ntnu.edu.tw -

#5.八位元畫家(8bit Painter) - Google Play 應用程式

在日本的Google Play 上被選為“Editor's Choice”。超過2,000,000 次下載。 八位元畫家(8bit Painter) 易於記憶,因為它縮小到直觀的操作方法和創建像素藝術所需的最少 ... 於 play.google.com -

#6.基本資料型態

Bit 是記憶體的最小儲存單位,由於電腦硬體結構的定址緣故, ... 一個Word可能等於2個bytes(16位元電腦)、4個bytes(32位元電 ... 以8位元來表示正負整數時,. 於 140.121.160.124 -

#7.第3 章影像媒體

8位元 灰階影像裡的每個像素包含一個0至255之間 ... 為最簡單的彩色模式,需要4 個位元(=16)來表示一 ... 位元。 ▫ 通常16色跟256色的影像都需搭配一個調色盤,每個顏. 於 www.csim.scu.edu.tw -

#8.記憶體

1.位元(BIT). 位元是計算機儲存資料的最小單元。位元是二進位位元(binary digit)的縮寫。 · 2.位元組(Byte). 把8個位元組合成一個單位稱為位元組,一個Byte共有 種不同的 ... 於 www.chwa.com.tw -

#9.HT66F2390技術訓練課程 - Holtek MCU

2021盛群盃8-Bit MCU介紹. HT66F2390 ... A/D : 12-Bit×16 Channels,內建固定的參考電壓(VBGREF) ... HIRC提供8、12、16MHz的系統頻率;由於IC內部併入了頻率補償. 於 mcu.holtek.com.tw -

#10.物件導向程式設計

8 個位元構成一個位元組(byte),在C/C++語言中,我們使用char(字元)資料型別來表示byte。例如一個字元的變數值可能包含位元如下: 01101100。 如果用16進位(hexadecimal) ... 於 ccy.dd.ncu.edu.tw -

#11.色彩簡介

如果使用16位元來記錄色彩,則可以記錄2^16 = 65536個色彩,而使用24位元,則可以 ... 位元的色彩解析度,其使用24位元的true color為基礎來描述色彩,並加上8位元的 ... 於 openhome.cc -

#12.16-bit - Translation into Chinese - examples English - Reverso ...

Translations in context of "16-bit" in English-Chinese from Reverso Context: Thumb-2 instruction ... Support 8-bit 60MHz and 16-bit 30MHz parallel interface. 於 context.reverso.net -

#13.8-bit、10-bit、12-bit、4:4:4、4:2:2、4:2:0 是什麼 ...

什麼是色深– 8-bit、10-bit、12-bit. 色深(Color Depth)亦可稱為色位深度,是指每個像素可以顯示的色階數,並以位元(bit) 數表示數位影像色階數目的單位。 於 www.datavideo.com -

#14.資料表示法

8 ). 種狀態變化。 2. 位元組(Byte)是在記憶體儲存裝置中經常使用到的容量表示單位,不過因為 ... 一個字組(word)等於2個Bytes(16位元電腦)、4個Bytes(32位元電腦)、8個. 於 greatbooks.com.tw -

#15.第零章進入64 位元

當時有許多廣告宣稱它是64 位元的CPU ( 至今還是有些書仍然如此寫)。 ... 雖然是在64 位元系統中,但是還是可以使用32、16、8 位元的暫存器,如上圖所示,小木偶列出 ... 於 wanker742126.neocities.org -

#16.最新消息:8位元深度與24位元深度png圖檔比較 - 中壢網頁設計

位元 深度是指影像中每一個像素包含多少色彩資訊可用,暫時先撇除32位元(註1.)來做解說,RGB影像是由3種色彩色版所構成﹝8BITS PER CHANNEL,不含alpha色板 ... 於 www.kip.com.tw -

#17.PhotoShop - 健豪印刷

點陣圖的解析度dpi值為300~350,色彩模式為CMYK,Photoshop影像位元數為8位元。 1.製稿時,請開一新檔,並將「影像尺寸 ... 於 www.gding.com.tw -

#18.位元深度 - 中文百科知識

位元 深度(BIT DEPTH)量化在調色盤(COLOR PALETTE)中有多少獨特的顏色,使用數字0和1,用於指定每個顏色 ... 標準JPEG文檔和TIFF文檔只能使用8位元和16位元每頻道。 於 www.easyatm.com.tw -

#19.【股海大丈夫】MCU族群天天漲但是這檔隱藏版MCU ... - 鉅亨

MCU 主要可分為8 位元、16 位元、32 位元,其中8 位元屬於低階的微控制器,主要應用於冰箱、洗衣機、烘乾機、低階馬達等,特色是成本低、功耗具優勢; ... 於 news.cnyes.com -

#20.8位和16位颜色的区别- 对照区别 - 有区别

在8位颜色中,单个像素可以具有256种可能的颜色中的任何一种(28),而在16位颜色中的单个像素可以 ... 本文链接:http://www.vsdiffer.com/8-bit-vs-16-bit-color.html 於 www.vsdiffer.com -

#21.Bit and Byte? - iT 邦幫忙

電腦記憶單位Bit由0或1, 請問0或1即是代表什麼? 而Byte相等於一個英文字 ... Byte 以以前8位元處理器去定義. ... 1 word = 2 Bytes =16 bits → 一個中文字 1 Byte = 8 ... 於 ithelp.ithome.com.tw -

#22.整數的數字型別- C# 參考

7 天前 — byte, 0 至255, 不帶正負號的8 位元整數, System.Byte. short, -32,768 至32,767, 帶正負號的16 位元整數, System.Int16. 於 docs.microsoft.com -

#23.影像格式JPEG vs RAW vs TIFF哪種較好?

TIFF的位元色深達16-bit,對於要作大量後期處理的影像有利。 ... 跟12-bit RAW及16-bit TIFF 相比,8-bit JPEG影像中主體上的花紋細緻度遜於12-bit ... 於 photo.popart.hk -

#24.計算機系統,16位,32位,64位什麼意思 - 嘟油儂

16 位、32位、64位等術語在作業系統理論中主要是指儲存器定址的寬度。 ... 位二進位制數是最基本的計算機語言,一個八位二進位制數也就是一個位元組。 於 www.doyouknow.wiki -

#25.一般在ps調圖,jpg格式是多少BIT?相機檔案16BIT的意義是 ...

jpg格式的影象檔案,屬於8位(8bit)影象檔案,16bit的影象檔案常見的是tiff格式檔案。 這裡的8位、16位,也稱作為“色深”,是指計算機用來儲存影象色彩 ... 於 www.juduo.cc -

#26.Ch.2 數字系統 - 李官陵彭勝龍羅壽之

用來表示這兩種狀態的單位,我們稱之為位元(bit)。 ... 一個字組包含了2 個位元組,共有2 × 8 = 16 個位元 ... 利用8 位元儲存整數能表示的正數範圍. ◦ (00000000). 於 web.csie.ndhu.edu.tw -

#27.[請益] 為什麼電腦資料要用16進位- 精華區ask-why

06/02 22:34. → kenin:8進位=3個bit 16進位=4bit 32進位=5bit 06/02 22:39. → yhliu:有的電腦系統是採用8進位的, 當然基礎仍是2進位. 06/02 22:45. 於 www.ptt.cc -

#28.photoshop開8位元與16位元色彩的差異?

拿8位元的色彩模式的圖檔去開銅版印刷和拿16位元色彩模式的去印會有很大的差異嗎? 或問的有些蠢.. 急 需 解 答 -- [1;30;40m夫兵者不祥之器物或惡之故有道者不處君子居 ... 於 tw.bbs.sci.design.narkive.com -

#29.第2章數位資料表示法 - SlideShare

Binary to hexadecimal and Hexadecimal to binary transformation 2-15 二進位轉十六. 十六進位轉二進位2-17 基底轉換法__十進位. 八進位A 3-bit pattern can be ... 於 www.slideshare.net -

#30.變更影像的色彩模式 - Corel Corporation

黑白(1 位元) · 灰階(8 位元) ; 色盤式(8 位元) · 色盤式(8 位元) ; RGB 色彩(24-bit) · LAB 色彩( 24 位元) ; CMYK 色彩(32 位元) · 多色頻 ; 灰階(16 位元) · RGB 色彩(48-bit) ... 於 product.corel.com -

#31.中文詞彙地區差異比較——#11「字節」與「位元組」 - Beyond ...

「比特」或「位元」的英文是「bit」,「bit」是英文「binary digit」的縮寫,即二進制數位,對應到電路中就是0/1的表示。「bit」是數據的最小單位,常見於 ... 於 byvoid.com -

#32.好和弦教你做8-bit 音樂!懷舊電玩風~ - YouTube

How to make 8 - bit music? [English CC]. 34,706 views34K views. Premiered Mar 7, 2020. 2.7K. Dislike. Share. Save. NiceChord (好和弦). 於 www.youtube.com -

#33.印前完稿需知 - 印樂事印刷網

發稿前,請留意是否為CMYK及8位元,RIP尚無法完整解釋16位元的檔案,易發生錯誤。 3.Photoshop檔案不能分圖層,請每一面一個檔案,並且為一個圖層,如分圖層等於文字未 ... 於 www.eve.com.tw -

#34.進制簡介(二進制、八進制、十進制、十六進制) - NotFalse 技術客

由於,幾乎所有計算機的資料大小,都是4位元的倍數, 且相對於十進制,二進制與十六進制(Hexadecimal, Hex) or 八進制(Octal, Oct) 的轉換, 更加地 ... 於 notfalse.net -

#35.如何辨別是16 位元或32 位元的應用程式? | Sony TW

1. 若想要的程式已經在執行,按下CTRL + ALT + DEL ,再點選Windows 工作管理員。 2. 點選處理程序標籤。 3. 若執行16 位元程式,在影像名稱欄位將找到Ntvdm.exe 的 ... 於 www.sony.com.tw -

#36.PCM格式介紹 - 台部落

Later Sound Blaster cards were capable of playing back 16-bit audio data. However, while these cards still played unsigned 8-bit PCM data, ... 於 www.twblogs.net -

#37.2個8位資料和一個16位資料相互轉換

這種位的轉換其實理解了本質就很容易了,也很基礎。 首先先了解一下bit和Byte,俗稱大B和小b的區別。 一個小b只能代表一個內容(0或者1,其中的一個) 於 www.itread01.com -

#38.8位, 16位,24位,32位圖片顯示原理及對比 - Medium

我們都知道一張圖片可以保存為很多種不同的格式,比如bmp/png/jpeg/gif等等。這個是從文件格式的角度看,我們拋開文件格式,看圖片本身,我們可以分為8位, 16位, ... 於 medium.com -

#39.16-bit Embedded Control Solutions Brochure (DS01032B_TW)

16 個16-bit通用暫存器. 軟體堆疊. 16 x 16分數/整數乘法器. 32/16與16/16除法. 40階多位元快速位移器. DSC系列增加功能(dsPIC30F與dsPIC33F):. •加入8個基本DSP指令. 於 ww1.microchip.com -

#40.AX92920 - 艾訊

M.2 Key E Module for 16-bit DIO. ... 產品特色. Two 8-bit TTL Level DIO ports with +5V powered; Programable DIO; 22 x 30 mm ... 於 axiomtek.com.tw -

#41.8位元16位元

由任天堂(NES)和世嘉Sega 所帶領,「8位元時代」從大約1985年持續到1990年早期16位元主機系統的崛起。 「8位元」名詞的普遍出現是因為下一代的遊戲主機廣告所導致的 ... 於 www.chisoku.me -

#42.16 bit 灰階 - 軟體兄弟

16 bit 灰階, 16 位元影像的Photoshop 支援. Photoshop 提供下列支援,以處理16 bpc 影像︰. 使用灰階、RGB 色彩、CMYK 色彩、Lab 色彩及多重色版模式。, 目前,16-bit ... 於 softwarebrother.com -

#43.NW-A55/A55HN/A56/A56HN/A57 | 說明指南| 支援的格式

輸出轉換為線性PCM的音訊。 APE ( .ape). 8位元,16位元,24位元/ 8 kHz - 192 kHz(快速,一般, ... 於 helpguide.sony.net -

#44.計算機概論(bit byte word ....的轉換)

所以它們之間的關系為: bit 可以代表0,1 1byte = 8 bits 1word = 2 bytes = 16bits 1doubleword = 2 words = 4bytes = 32bit ... 於 note1.pixnet.net -

#45.二、八、十與十六進位(數字系統) 轉換教學 - 腳印網頁資訊設計

有效位. 最高有效位( MSB ):表示最左邊的位元→ 1010。 最低有效位( ... 於 www.footmark.com.tw -

#46.8 位和16 位图像- MATLAB & Simulink - MathWorks 中国

双精度(64 位)浮点数是数值数据默认的MATLAB ® 表现形式。但为了降低使用图像的内存需求,您可以分别使用数值类 uint8 和 uint16 将图像保存为8 位和16 位无符号整数 ... 於 ww2.mathworks.cn -

#47.雜專欄:關於「8位元」世代 - Engadget

在電視遊戲的說法,「8位元」指的是在1980年代中期的電視遊戲主機普遍世代。由任天堂(NES)和Sega所帶領,「8位元時代」從大約1985年持續到1990年早期16 ... 於 chinese.engadget.com -

#48.請問photoshop 的8位元色版與16位元色板是什麼意思 ... - 隨意窩

請問photoshop 的8位元色版與16位元色板是什麼意思呢?這是描述影像深度的解析數值,目前全彩的色彩多以24位元來表現,可以達到1600多萬色~~~以下是相關的參考資料:8 ... 於 blog.xuite.net -

#49.【股海大丈夫】MCU族群天天漲但是這檔隱藏版 ... - 奇摩新聞

MCU 主要可分為8 位元、16 位元、32 位元,其中8 位元屬於低階的微控制器,主要應用於冰箱、洗衣機、烘乾機、低階馬達等,特色是成本低、功耗具優勢; ... 於 tw.stock.yahoo.com -

#50.微控制器產品技術與新興應用

4位元. 冰箱、洗衣機、微波爐等家電控制. 8位元、16位元. 一般的控制領域. 一般不使用作業系統 ... 8 bit. • 8051, 6502, PIC, … – 16 bit. • TI MSP430, … – 32 bit. 於 cse.nsysu.edu.tw -

#51.19-3 8-bit 影像

在MATLAB 第5 版之後,提供了uint8 的資料型態,因此可以將儲存空間降為原先的八分之一。(uint8 代表8-bit unsigned integer,即是8 位元、不帶符號的整數值。). 於 mirlab.org -

#52.photoshop RGB模式裡面8位、16位、32位各適合什麼 - 壹讀

為你找了個答案:色域指電腦上色彩顯示的範圍上面的數字都是指2的指數即可顯示從〇到2的若干次的色彩變化比喻來說,8位指的是「木頭」,密度低, ... 於 read01.com -

#53.132.8 位元/色版RGB 色彩模式影像的位元深度為?(A)8 位元(B)1..

132. 8 位元/色版RGB 色彩模式影像的位元深度為? (A)8 位元 (B)16 位元 (C)24 位元 (D)32 位元。 於 yamol.tw -

#54.何謂光的三原色?

波塞頓Z【RGB全彩炫光】採用最新型32位元ARM CORTAX-M0架構微型控制器與最新16位元MCU技術,並結合三顆單鍵LED 背光控制器,個別控制紅光、綠光以及藍光,玩家能經由 ... 於 tw.ttesports.com -

#55.第三章研究背景

P15 16 個bit,其中P15 為P14 的進位(carry)。 圖22 為8 × 8 bit Baugh-Wooley 正負號乘法,其中NSi,j=NOT. (Xi AND Yj)。與8×8 bit 無正負號乘法比較,Baugh -Wooley ... 於 ir.nctu.edu.tw -

#56.8Bit vs. 16Bit | Bit Depth | What is Tonal Range? - The Art of ...

What is the difference between editing images in 8-bit or 16-bit? While it should be obvious that 16-bit color is significantly better than ... 於 www.theartofretouching.com -

#57.轉換數制, 十六進制

使用這個簡單的工具快速轉換十六進制作為數制的單位. 於 www.convertworld.com -

#58.八位元MCU的創新變革與應用:MCU,時脈,笙泉科技 - CTIMES

回顧微控制器(MCU)的演變歷程,可說是從早期4/8位元(bit)經歷過度的16 bit,直到近年非常普及的32 bit。不論在運算時脈、串列周邊與類比輸入輸出 ... 於 www.ctimes.com.tw -

#59.解释颜色深度概念:8 bit、16 bit、32 bit的意思 - CSDN博客

也就是从0到255,用二进制表示就是从00000000到11111111,总共需要8位二进制数,所以颜色深度是8 Bit。 (2)如果是BMP格式,则最多可以支持红、绿、 ... 於 blog.csdn.net -

#60.位元、位元組以及K, M, G, T - 運算與程式設計 - GitBook

現代的電腦使用了二進位數字系統作為其基本的計量單位,為什麼是二進位呢?那麼什麼又是位元bit、位元組Byte呢?KB、MB、GB、TB又分別代表什麼意思呢? 於 nkust.gitbook.io -

#61.Photoshop 的8位元與16位元色版| 99(一)實踐大學數位影像創作

郭慧禪Hui-Chan Kuo: Photoshop 的8位元與16位元色版help.adobe.com/zh_TW/photoshop/cs/using/WSfd1234e1c4b69f3... RGB 色彩模式Photoshop RGB 色彩 ... 於 www.flickr.com -

#62.淺談位元色版color channel - OXXO.STUDIO

那什麼是photoshop 中的8 位元16 位元與32 位元呢? color channel. 若以8 位元的RGB 色版為例,則是R 色版具有2^8 = 256 種紅色( 0~255 ),G 色版與B 色版也各具有256 ... 於 www.oxxostudio.tw -

#63.如何將24-bit 顏色轉換成16-bit 顏色 - allenchak

24-bit 由三原色,紅綠藍所組成,每色8-bit,即0 – 255,數字代表顏色深度。為減少數字長度,會換成16 進制先。 例如紫色,由紅色加藍色,所以RGB(255 ... 於 allenchak.wordpress.com -

#64.Microcontrollers - 松翰科技

松翰的微控制器除原有8位元外,也已跨入32位元的領域,可提供給客戶功能更強大,運算效能更優越的最佳選擇。 目前松翰的微控制器已廣泛應用於電腦周邊裝置、通信產品、 ... 於 www.sonix.com.tw -

#65.Microchip Technology AVR® XMEGA™ 8-Bit & 16 ... - Mouser

Microchip Technology AVR® XMEGA™ 8-Bit and 16-Bit Microcontrollers (MCUs) are low power, high performance, and peripheral rich MCUs based on the AVR ... 於 www.mouser.tw -

#66.利用二位元數位比較器實現之8 位元數位比較器

相較於傳統之8 位. 元數位比較器,本論文提出之8 位元數位比較器具. 有易於擴充,以及平均延遲時間較少之優點。本論. 文提出之電路經由HSPICE 電路模擬軟體模擬,在. 使用 ... 於 nfudee.nfu.edu.tw -

#67.第一章單晶片微電腦簡介

addr16 16 位元 位址常數,使用於LCALL 及LJMP 指令。 rel. 8 位元偏移位址常數,使用於SJMP 及相對跳躍指令中。 bit. 位元定址位址。 ←. 以右方資料取代左方資料。 於 www.slvs.ntct.edu.tw -

#68.數字系統與資料表示法

位、二進位、八進位、十六進位數字系統要如何轉換,彼此才能看得懂嗎? ... Bit. 位元. Bits. 最小的單位. Byte. 位元組. Bytes. 1Byte=8Bits. KB. 仟位元組. 於 www2.lssh.tp.edu.tw -

#69.HY17P4x/5x | 紘康科技

數位特性: 8-Bit RISC-like微控制器. 具有71條高性能指令集H08D; 硬體乘法器及查表器; Power On/ Brown Out 1/ Brown Out 2 Reset; 支援C及Assembly編譯環境. 於 www.hycontek.com -

#70.影像處理基本概念像素「像素」pixel 是Photoshop 中影像的 ...

若影像是灰階模式、RGB 模式或是CMYK 模式的話,您可以選用16-bit 色. 彩而不要採用預設的8 位元色彩。在預設的情況下,利用上述三種模式色頻組成. 之影像將包含256 階灰階 ... 於 eportfolio.lib.ksu.edu.tw -

#71.色彩深度

3位元:8種顏色,用於大部分早期的計算機顯示器。 4位元:16種顏色,用於EGA及不常見及在更高的解析度的VGA標準,color Macintoshes。 於 www.wikiwand.com -

#72.什麼是D/A轉換器?:數位的世界採用2進位

3bit=8階4bit=16階5bit=32階6bit=64階7bit=128階8bit=256階 9bit=512階11bit=2048階12bit=4096階14bit=16384階16bit=65536階. 【什麼是bit】 是代表2進位的位元(binary ... 於 www.rohm.com.tw -

#73.颜色模式中8位,16位,24位,32位色彩是什么意思?会有什么区别 ...

常见的颜色有8位16位24位32位色,其中24位及以上称为真彩,是PC上最常用的颜色,其他基本用于嵌入式系统或一些工控领域,详情可查阅一下表格:. Bit- ... 於 www.cnblogs.com -

#74.掃描器相關技術名詞解釋 - 數位蘋果網

256 階的灰階足以真實的呈現出比肉眼所能辨識出來的層次還多的灰階層次。 24 位元彩色(24-bit color). 24 位元彩色影像由三個8 位元的彩色通道所組成 ... 於 www.fuji.com.tw -

#75.你所不知道的C 語言:bitwise 操作 - HackMD

位元 運算會忽略填充位元,因此(等級不低於unsigned int 的)無號整數可安心使用。為求最大可攜性,位 ... assuming 16 bit, 2-byte short integer, two's complement: 於 hackmd.io -

#76.數字系統

7 位數編碼ASCII 如:A 100 0001→7 位數;編碼方式不同產生. 亂碼問題. ○ 因應英文語系的應用,採8 位元編碼,如:A 0100 0001. ○ Unicode → 16 位元編碼;因應網際 ... 於 web.cjcu.edu.tw -

#77.Atmel Tiny88 16-bit Timer - 解甲歸田

16位元 計時器的方塊圖 · Timer/Counter 1 (TCNT1) - 計數器/計時器#1 · Output Compare Register (OCR1 A/B) - 比較器暫存器#1 A/B 輸出,計數值和目標值 ... 於 andychen15577.blogspot.com -

#78.photoshop 常用影像檔案格式 - JOYCAT 電腦教學

至於大於2 GB 的檔案,請儲存為大型文件格式(PSB)、Photoshop Raw (僅限平面化影像)、TIFF (最大4 GB) 或DICOM 格式。 影像的標準位元深度是每個色版8 位元。若想使用16 或 ... 於 joycat.org -

#79.ps中cmyk顏色模式8位和16位的區別

ps中cmyk顏色模式8位和16位的區別,1樓江南沐子8位通道中包含256個色階, ... 顯示或列印畫素,其單位是“位(bit)”,所以顏色深度有時也稱為位深度。 於 www.bees.pub -

#80.109 學年度第2 學期第1 次期中考< 微處理機> 試卷

同等對待(D) 所有Memory 的指令皆可以用來做I/O 的. 工作. 36.【 C 】一般8 位元的微電腦系統是以16 位元來表示位址. (Address),則該微電腦系統有____個位址空間. 於 sps2013sp1.shinmin.tc.edu.tw -

#81.C語言中,為什麼64位下指針變成8位元組? - GetIt01

首先,我們得知道另一個計算機常識,那就是,一個位元組(byte)佔用多少位(bit),沒錯,是8位。這裡,你可能會發現一個有趣的地方,32 bit == 4 byte , 64 == 8 byte。 於 www.getit01.com -

#82.【LIBERTY】8位元計算機(顏色隨機出貨) - momo購物網

#16位數 · #8位數 · #14位數 · #LIBERTY · #CASIO 卡西歐 · #12位數. 於 m.momoshop.com.tw -

#83.位元深度和偏好設定- Adobe Photoshop

此外,也瞭解位元深度如何影響影像大小,以及如何更改位元偏好設定。 ... 除了8 位元/色版的影像外,Photoshop 也可以處理包含16 或32 位元/色版的 ... 於 helpx.adobe.com -

#84.色彩16 bit 同32 bit 有乜分別??? - 吹水台 - 香港高登

8位元 : 256種顏色,用於最早期的彩色Unix工作站,低解析度的VGA,Super VGA,AGA,color Macintoshes。灰階,有256種灰色(包括黑白)。若以24位元 ... 於 forum.hkgolden.com -

#85.晶片音樂 - 萌娘百科

晶片音樂(英語:Chiptune 或Chip Music),又名8位元機音樂(英語:8-Bit ... 這支樂隊的很多音樂對後來的8位元和16位元的電動遊戲平台的音樂同樣造成了很大影響。 於 mzh.moegirl.org.cn -

#86.16 Bits vs 8 Bits 修圖結果大不同- Photoshop 入門教學

無容置疑16-bit 比8-bit 位元深度提供更多色階。 究竟16-bit 比8-bit 通道(Channel)多出多少色階呢?以單一通道(如紅色)計,16-bit 可提供2 的16 次方,即65536 種色調 ... 於 www.imagejoy.com -

#87.攝影家手札Forum- 《器材版》16-bit檔案是否優於8-bit檔案?

以下翻譯Dan Margulis新書Photoshop LAB Color的幾段文字(第133頁),算是下雨天,給各位解解悶吧! 16-bit檔案是8-bit檔案的兩倍大,前者每頻道有65,536 ... 於 www.photosharp.com.tw -

#88.什麼是8bit?10bit?詳解色彩深度(位元率)與動態範圍的關係

在數位設備的儲存中,所有資訊都是以「位元」(bit)為單位來表達。 ... 方),所以可以儲存16個光訊號;8bit就能儲存2 8(二的八次方),等於256 ... 於 www.jjfilm.com.tw -

#89.色彩深度- 维基百科,自由的百科全书

3位元:8种颜色,用於大部分早期的计算机显示器。 4位元:16种颜色,用於EGA及不常見及在更高的分辨率的VGA标准,color Macintoshes。 於 zh.wikipedia.org -

#90.電子遊戲異聞錄:8位主機、16位主機,我們到底在說什麼?

主機上印著大大的16-bit字樣就是為了和FC分庭抗禮,因為FC屬於8-bit遊戲機,在玩家選購的時候當然會傾向於更強勁的主機性能,畢竟數碼產品買新不買舊 ... 於 kknews.cc -

#91.[教學]Unicode 是用幾個位元來進行編碼?

ASCII 碼使用8 位元編碼、 BIG-5 碼與Unicode 都是使用16 位元編碼。 ... UTF-8 使用1 至6 個位元組( 8 ~ 48 bits ) 儲存一個文字。 於 lsslab.blogspot.com -

#92.PCIE-1812 - 250 kS/s, 16-bit, 8-ch, Simultaneous Sampling ...

The devices can simultaneously sample 8 AI channels with differential input ... 250 kS/s, 16-bit, 8-ch, Simultaneous Sampling, Multifunction PCIE Card. 於 www.advantech.tw -

#93.新手海報製作問題 - Mobile01

開300dpi CMYK模式後面8位元跟16位元我不知道有什麼差別? 海報是舞會的宣傳海報而以。可是這樣開下來檔案就300多MB,電腦也跑不動。調個特效就說 ... 於 www.mobile01.com -

#94.C語言:變數- 字面常數

char一般是8位元,有可能是16位元,依實作而定。 short:短整數(short integer),可以是有號或無號,預設(default)是有號。如果需要無號,請在前面加unsigned。例如: 於 lth.name -

#95.8位元英文 - 英語翻譯

8位元 英文翻譯: 8-bit…,點擊查查綫上辭典詳細解釋8位元英文發音,英文單字,怎麽用英語翻譯8位元,8位元的英語例句用法和解釋。 於 tw.ichacha.net -

#96.組合語言指令格式

8位元 之位址碼,可以代表內部RAM中較低的128個位元組之位址(0~127)或特殊功能暫存器 ... 包含在指令中的8位元常數資料。 # data 16. 包含在指令中的16位元常數資料。 於 imod-fms.csu.edu.tw -

#97.32位元MCU夯新唐盛群沾光- 工商時報

法人看好,切入32位元MCU市場的新唐(4919)、盛群(6202)等供應鏈將可望 ... 不過,16位元及8位元等MCU表現相對平淡,IC Insights指出,16位元MCU ... 於 ctee.com.tw